Balita

Tinutukoy ng DAC ang papel ng AI at ML sa mga merkado

Ang Moscone Center, San Francisco, ay tatanggapin ng DAC 25-28 Hunyo

OneSpin Solutions at Austemper Design Systems ay parehong i-highlight ang mga tool para sa functional na pagpapatunay sa kaligtasan. Ang Austemper ay tumututok sa pag-unlad ng kritikal na misyon ng sistema, kasama ang KaleidoScope tool suite na sumusuporta sa analogue na disenyo para sa kasabay, mixed-signal fault propagation. Ang automated tool suite ay may kaligtasan na pagtatasa, synthesis at mga kakayahan sa pag-verify para sa mga application na nakatuon sa certification. Ito ay ginagamit para sa malakihang mga disenyo ng automotive sa ADAS at nagsasarili sa pagmamaneho. Ang kasabay na kunwa kasalanan ay kinabibilangan ng mga simulation na inirerekomenda ng ISO 26262 upang sumunod sa mga kinakailangan ng ASIL.

Ang kumpanya kamakailan nakipagsosyo sa OneSpin Solutions upang magpatibay ng isang pamamaraan na suportado ng tool para sa mga functional na application sa kaligtasan, pagsasama ng isang daloy ng disenyo at pag-verify, na ipapakita sa booth ng OneSpin. Ang mekanismo ng kaligtasan ng hardware ay ipinasok sa mga disenyo ng maliit na tilad at ang mga tool ng OneSpin Solutions ay pormal na nagpapatunay sa lohika sa kaligtasan ng hardware. Tinitiyak ng pag-check sa katumbas na ang hindi nakakaapekto sa lohika sa kaligtasan ay hindi nakakaapekto sa regular na pag-andar at pagsusuri ng pagtuklas ng kasalanan ay nagpapatunay na ang mga mekanismo ng kaligtasan ay gumaganap ng maayos sa kaganapan ng mga random na error.

Ang OneSpin ay nagpo-promote din ng Kit Tool Qualification nito, kasunod ng pagpapatunay ng TÜV SÜD ng mga proseso ng pag-unlad ng tool nito. Ang paunang kit ay magagamit para sa 360 EC-FPGA EDA tool ng kumpanya, isang awtomatikong sequential pagkapareho tseke na pumipigil sa daloy ng disenyo ng FPGA mula sa pagpapasok ng mga error sa pagpapatupad. Ang kit ay sertipikado sa ISO 26262, IEC 61508 at EN 50128.

Mga pananaw ng FPGA

Pa rin sa FPGA disenyo, Magpawalang-saysay ay nakipagtulungan sa Xilinx upang mag-alok ng Vivado design suite sa cloud, sa pamamagitan ng Plunify Cloud platform. Ang mga taga-disenyo ay magbabayad nang kasing dami ng 50c upang itala ang isang proyekto ng Vivado sa cloud ng Mga Serbisyo sa Amazon (AWS), kabilang ang mga lisensya.

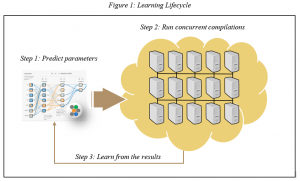

Ipapakita rin ng kumpanya ang mga pagpapahusay sa software na pagsasara ng InTime timing nito upang ma-optimize ang FPGA timing sa cloud (Figure 1). Maaaring mapabuti ng InTime Optimization Methodology ang dalas ng orasan sa pamamagitan ng 20 hanggang 80% at matugunan ang mga kinakailangan sa pag-time sa mga araw, sa halip na mga linggo sa pamamagitan ng pag-aaral ng machine. Pinapabilis din ng software ang pagsasara ng oras at pag-optimize at ina-access sa pamamagitan ng cloud.

Ipapakita rin ng kumpanya ang mga pagpapahusay sa software na pagsasara ng InTime timing nito upang ma-optimize ang FPGA timing sa cloud (Figure 1). Maaaring mapabuti ng InTime Optimization Methodology ang dalas ng orasan sa pamamagitan ng 20 hanggang 80% at matugunan ang mga kinakailangan sa pag-time sa mga araw, sa halip na mga linggo sa pamamagitan ng pag-aaral ng machine. Pinapabilis din ng software ang pagsasara ng oras at pag-optimize at ina-access sa pamamagitan ng cloud.

Pag-promote ng teknolohiya ng eFPGA, Achronix Semiconductor nakikipagtulungan sa espesyalista sa IP CAST upang madagdagan ang throughput at gumawa ng mga pagtitipid sa memory imbakan.

Ang dalawang exhibitors ay magpapaliwanag kung paano ang port lossless compression ng CAST ay na-port sa portfolio ng Achronix FPGA para gamitin sa data center at mga mobile na gilid ng mga application ng paglipat ng data. Ang pagpapatupad ng hardware ng standardless compression standard para sa Deflate, GZIP at ZLIB, ay katugma sa mga pagpapatupad ng software na ginagamit para sa compression o decompression upang magbigay ng hanggang 100Gbit / s throughput na may mababang compression at mababang latency, kaisa sa Speedcore eFPGA technology upang ilipat at mag-imbak ng malaki data sa mababang paggamit ng kuryente.

Ipinadala ng CAST ang IP nito sa mga FPGAs ni Achronix

Kahusayan ng enerhiya

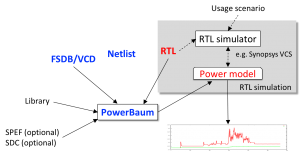

Nagsasalita ng pamamahala ng kuryente, isa pang nagtatanghal, Baum, kinikilala ang enerhiya na kahusayan bilang ang pinaka-ilalim na lugar sa disenyo ng maliit na tilad. Ang automated power analysis at modeling tool ay dinisenyo para sa automotive, IoT, mobile, networking at mga proyekto ng server. Ang PowerBaum 2.0 (Figure 3) ay sumusuporta sa dynamic at static na kapangyarihan, kumukuha sa mga paglalarawan ng RTL at netlist, at nagdaragdag ng suporta para sa pagtatasa ng kapangyarihan sa pagtulad ng hardware. Ito, sabi ng kumpanya, ay nagbibigay-daan sa mga inhinyero na ayusin ang mga bug sa kapangyarihan sa makatotohanang mga sitwasyon ng software. Sinusuportahan din ng tool ang pagsusuri sa mga arbitrary na temperatura na tinukoy ng mga designer, upang masuri ang mga epekto ng temperatura sa paggamit ng kapangyarihan ng disenyo.

Sa DAC, ipakikilala rin ng kumpanya ang PowerWurzel, isang antas ng pagtatasa ng power level engine na isinama sa PowerBaum para sa pagmomodelo ng kapangyarihan.

Figure 3 Baum ng mga tool pag-aralan ang enerhiya na kahusayan

Ang disenyo at mga tool ng pag-verify ng SoC na batay sa Cloud para sa disenyo ng IC mula Mga Sukatan isama ang Cloud Simulator at Verification Manager, na dinisenyo upang pamahalaan ang mga kinakailangan at mapagkukunan ng kunwa, pag-aayos ng mga ito pataas o pababa bawat minuto. Ang kumpanya ay nag-aangkin na ang Google Cloud ay nagbibigay-daan sa walang limitasyong kapasidad ng kunwa ng SystemVerilog na sumusunod sa UVM at katutubong, pamamahala ng pagpapatunay na batay sa web para sa mas mabilis na mga oras ng pagbabalik, nababawasan ang mga error sa trunk code at ang predictable coverage ng code.

Bukod sa mga exhibitors, ang kaganapan ay nagho-host ng mga teknikal na session at isang programa ng mga keynote na tumutugon sa mga lugar na pangkasalukuyan. Sa taong ito, halimbawa, ang indayog ay magho-host ng isang tutorial sa 'Functional Safety at Reliability para sa Automotive Applications', at isa sa machine learning ('Machine Learning Dadalhin Pagganap ng Pagtatangi sa Pagsasalita sa Susunod na Antas'). Ang pangunahing tono ni Anna-Katrina Shedletsky, Instrumental, sa Lunes 25 Hunyo, ay tumutuon sa 'Automating Intelligence: Machine Learning at Future of Manufacturing'. Ang paggamit ng ML at AI para sa panlipunan assistive robotics (SAR) ay nauukol sa keynote ng Huwebes ni Maja Matarić, University of Southern California na magpapakita ng 'Automation vs Augmentation: Socially Assistive Robotocs and the Future of Work'.

Ang isa pang pangunahing tagapagtaguyod ay ang RISC-V bilang isang paraan para sa mga libreng arkitekto mula sa mga proprietary set architectures (ISAs). Si David A Patterson, Google at University of California, ay magpapakita ng 'Isang Bagong Golden Age para sa Computer Architecture: Mga Tukoy na Accelerators ng Domain at Buksan ang RISC-V'.

Ang isang bagong lugar sa taong ito sa DAC ay ang Design Infrastructure Alley. Ang inisyatiba ng ESD Alliance at Asosasyon para sa High-Performance Computing Professionals ay isang lugar na nakatuon sa imprastraktura ng IT para sa disenyo ng mga electronic system at mga sangkap. Pati na rin ang mga kinakailangang computing at imbakan para sa disenyo at pamamahala ng paggamit ng ulap, mayroong dedikadong Design-on-the-Cloud na pavilion theater na tinatalakay ang pamamahala ng lisensya, grid computing at seguridad ng data.